February 29, 2024

Members Only Series: Jens Hagemayer of Bielefeld University and the COM-HPC plus CXL Opportunity

COM-HPCOpen StandardsPICMGSlider

This issue we introduce Jens Hagemayer, a research associate at the Bielefeld University. Jens and his team have been intimately involved in the development of COM-HPC since its inception, championing the use of heterogeneous modules designed around FPGAs. Now they are investigating ways that Compute Express Link (CXL) specifications can take COM-HPC into new use cases.

PICMG: Can you describe your work outside of PICMG as well as the role you played in development of the COM-HPC specification?

JENS: I am currently engaged in research at Bielefeld University, focusing on the development of heterogeneous and reconfigurable computing technologies for a wide range of applications. These include the Internet of Things (IoT), edge computing, cloud computing, and high-performance computing (HPC).

My involvement with the early stages of the COM-HPC specification centered on leading the development of the Platform Management Interface Specification and expanding the Embedded EEPROM Specification for COM-HPC.

PICMG: You recently raised awareness about the CXL standard within the COM-HPC community. What is CXL and why is it relevant for PICMG COM-HPC developers and users?

JENS: CXL, or Compute Express Link, is a high-speed, high-capacity interconnect standard that facilitates efficient communication between CPUs, memory, and peripherals using the PCIe physical layer. Its support for cache coherency, disaggregation, and scalable architectures makes it a compelling choice for modular form factors like COM-HPC, driving its popularity among developers and users seeking advanced computing solutions.

PICMG: Why is CXL 3.1 significant in the context of COM-HPC? What use cases or capabilities will it drive in the COM-HPC ecosystem?

JENS: CXL introduces features that cater to the demanding requirements of cloud and high-performance computing systems. Its emphasis on scalable architectures, disaggregation, and cache coherency is particularly relevant for COM-HPC, offering the potential to revolutionize the way modular computing platforms are designed and utilized.

The integration of CXL into COM-HPC could facilitate the development of more sophisticated computing solutions, enabling the seamless coupling of specialized accelerators and the establishment of cache-coherent multi-socket systems. These advancements promise to unlock new possibilities for COM-HPC applications, ranging from data-intensive analytics to AI and machine learning workloads, driving innovation in modular computing technologies.

PICMG: Given that CXL targets PCIe, has it been compatible with COM-HPC to date?

JENS: The relationship between CXL and COM-HPC is fundamentally influenced by CXL’s reliance on the PCIe physical layer for connectivity. This means that while direct compatibility between previous versions of CXL and COM-HPC has not been explicitly defined, the architectural underpinnings allow for potential integration.

The absence of CXL in the current COM-HPC specification, coupled with the lack of support in existing modules, suggests that the integration of CXL represents a forward-looking opportunity for enhancing COM-HPC. Such integration is anticipated to require minimal modifications to the specification, paving the way for future advancements in modular computing.

PICMG: What does the COM-HPC community need to know about the CXL market or technical requirements to capitalize on the opportunity?

JENS: To fully leverage the potential that CXL brings to the COM-HPC community, it is crucial to understand the intricacies of CXL’s market dynamics and technical specifications. This involves a deep dive into the architecture of CXL, including its device types—such as Type 1 for I/O devices, Type 2 for cache-coherent devices, and Type 3 for memory expander devices. Additionally, understanding the topology options that CXL supports, including switch-based topologies for larger, more complex systems, can empower developers to design COM-HPC solutions that are both innovative and future-proof.

Staying abreast of the evolving CXL specifications and market trends will enable the COM-HPC community to identify new opportunities for integration and application, ensuring that COM-HPC modules remain at the forefront of technological advancement.

PICMG: What are you and Bielefeld University doing with respect to CXL today?

JENS: We are working on integrating CXL within the RISC-V ecosystem, a venture that holds promising implications for the future of computing architectures. Our work focuses on the development of innovative bridge technologies that facilitate communication between the RISC-V Coherent Hub Interface (CHI) and CXL, using FPGA-based modules, which we refer to as microservers.

This endeavor is not just about bridging two technical standards; it’s about creating a foundation for next-generation computing platforms that can seamlessly integrate diverse processing and memory resources. By developing these bridges, we aim to enable more efficient, scalable, and flexible computing architectures that can cater to the demanding requirements of modern applications, ranging from AI and machine learning to big data analytics.

PICMG: Where can interested parties go to find more information on CXL?

JENS: The CXL Consortium website serves as the primary repository of knowledge. This platform not only provides access to the official CXL specifications and technical documents, but also offers insights into the latest developments, industry adoption stories, and educational resources.

More Information:

• Compute Express Link: https://computeexpresslink.org

•*PICMG COM-HPC Overview: https://www.picmg.org/openstandards/com-hpc

•*PICMG Platform Management Interface Specification: https://www.picmg.org/product/com-hpc-platform-management-interface-specification

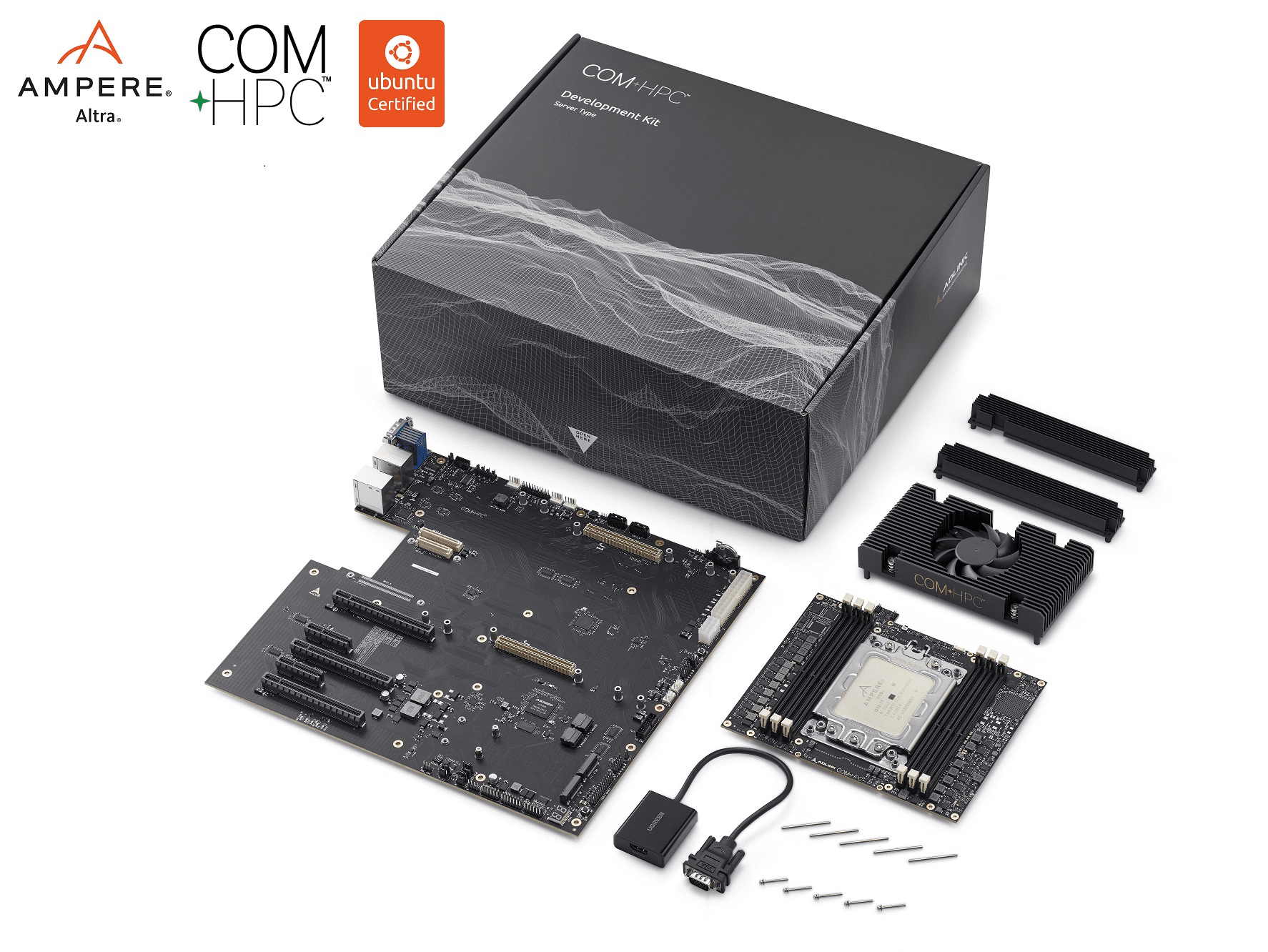

Figure 1. ADLINK performed eight weeks of testing on the

Figure 1. ADLINK performed eight weeks of testing on the